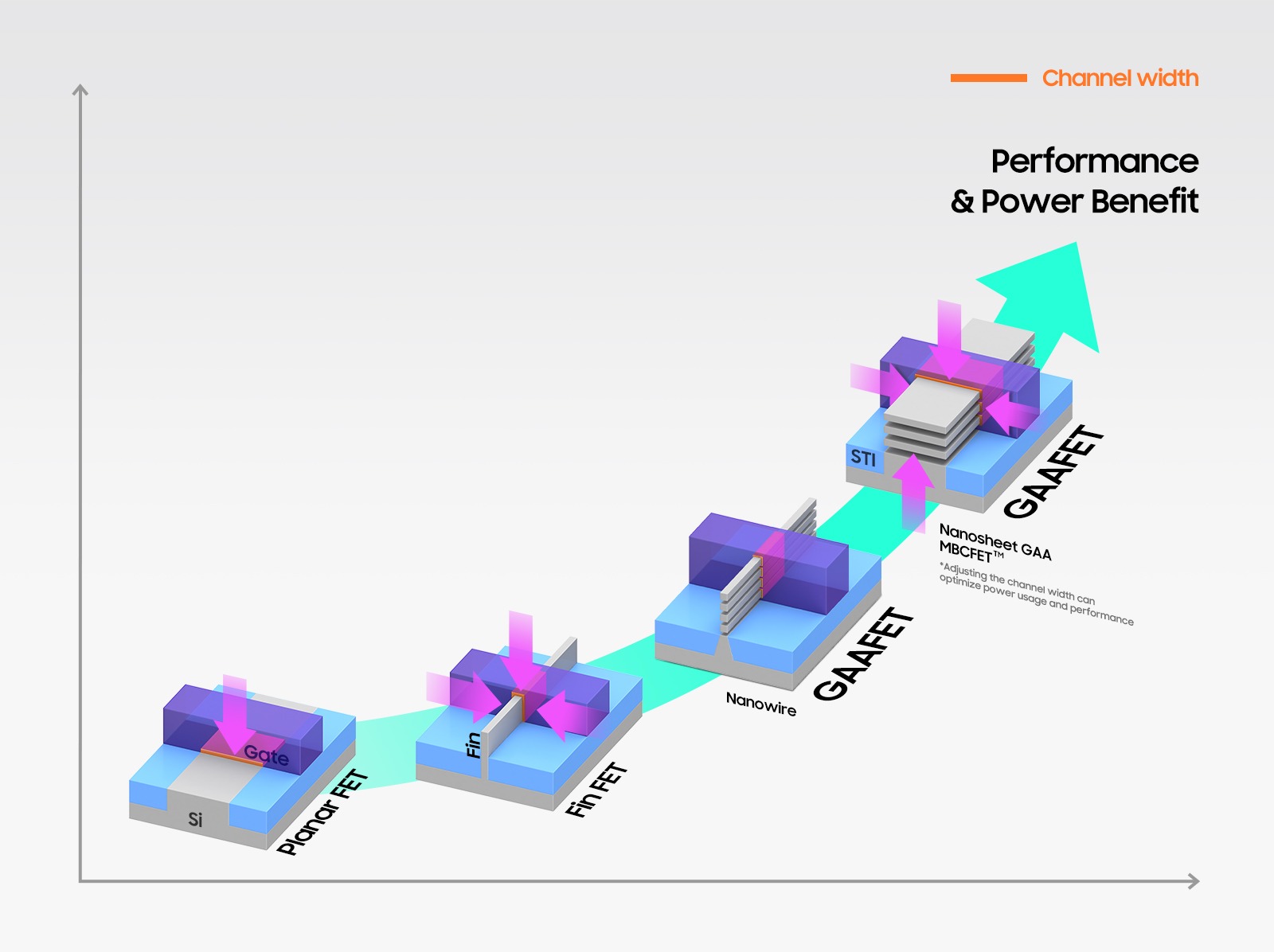

La división de semiconductores Samsung Foundry anunció que comenzó la producción de chips de 3 nm en su fábrica de Hwasong. A diferencia de la generación anterior, que utilizaba tecnología FinFet, el gigante coreano utiliza ahora la arquitectura de transistores GAA (Gate-All-Around), lo que aumenta significativamente la eficiencia energética.

Los chips de 3 nm con arquitectura MBCFET (Multi-Bridge-Channel) GAA obtendrán una mayor eficiencia energética, entre otras cosas, al reducir la tensión de alimentación. Samsung también utiliza transistores de nanoplacas en chips semiconductores para conjuntos de chips de teléfonos inteligentes de alto rendimiento.

En comparación con la tecnología de nanocables, las nanoplacas con canales más anchos permiten un mayor rendimiento y una mejor eficiencia. Al ajustar el ancho de las nanoplacas, los clientes de Samsung pueden adaptar el rendimiento y el consumo de energía a sus necesidades.

Te podría interesar

En comparación con los chips de 5 nm, según Samsung, los nuevos tienen un rendimiento un 23% mayor, un consumo de energía un 45% menor y un área un 16% más pequeña. Su segunda generación debería ofrecer entonces un 2% más de rendimiento, un 30% más de eficiencia y un área un 50% más pequeña.

“Samsung está creciendo rápidamente a medida que continuamos demostrando liderazgo en la aplicación de tecnologías de próxima generación en la fabricación. Nuestro objetivo es continuar este liderazgo con el primer proceso de 3 nm con la arquitectura MBCFETTM. Continuaremos innovando activamente en desarrollos tecnológicos competitivos y creando procesos que ayuden a acelerar el logro de la madurez tecnológica”. dijo Siyoung Choi, director del negocio de semiconductores de Samsung.